周末热议的 Chiplet ,会带火哪些半导体细分?

Chiplet 工艺对半导体产业链影响最大的是封装和测试环节,芯片设计是测试机需求的先验指标。

Chiplet 工艺对半导体产业链影响最大的是封装和测试环节,芯片设计是测试机需求的先验指标。

近日 Chiplet 的概念大火,作为延续摩尔定律的一个重要技术到底说了些什么?又会影响到半导体产业链的哪些环节?

首先,要了解到 Chiplet 是一种制造和封装芯片的方法。其最重要的技术突破在于封装,其次是测试。

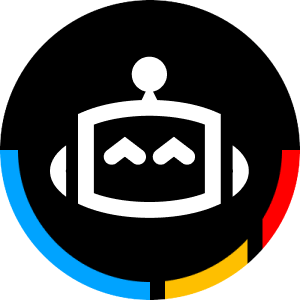

可作为对比的是:现在普遍采用 SOC 模式,从下图中可以清晰可见。两种工艺的不同指出在于,SOC 是把载有不同功能的模块都封装在同一晶圆中;而 Chiplet 是将模块进行归类划分,先封装成几个不同的裸片,最后再封装到一起。也就是说 Chiplet 比 SOC 多了一组封装的流程。

两种工艺的重点区别

首先,SOC 模块要求封装的必须是相同制程的模块,比如 GUP、CUP、存储都必须是 7nm 制程;

而 Chiplet 因为是进行分别封装的,所以对第一次集成裸片的工艺要求没有那么苛刻,比如说封装一个 7nm 的 CPU、14nm 的存储芯片,130nm 的模拟芯片,接下来就是最后一步,将这些已封装好的裸片再次封装到一起。

所以,最后一个封装环节就变得极为关键,因为要将不同工艺,或者不同材质的模块(比如 Si、SiC、GaN)集成在一起。这里会涉及到电路接口、信号传输、裸片位置放置的布局设计,就存在非常复杂的情况,对封装厂的技术有了更高的要求。

这也就是为什么要成立 Chiplet 生态联盟的重要原因之一。随着关键传输协议标准的形成、各个功能区域模块的链接方式统一,那么 Chiplet 的应用才可能被大范围推广。

测试需求显著增加

非常明显的是,Chiplet 要比 SoC 进行更多次的封装,也就需要进行更多次测试检验,以确保每个裸片都是可以正常运作的,不然一单存在单一模块性能失效,后面的封装也就是做无用功,所以多次检测的目的是为了能够提高出货良品率。

从晶圆上的裸片来看,理论上 Chiplet 的良率是会明显高于 SOC 的,因为要切割的模块单位面积变小了,晶圆上如果存在污染点对于模块影响的概率要降低一些。

而另一方面,Chiple 工艺在不同晶圆上切割下来的模块数量会更多,但是随着模块性能进行分类集成,对于芯片厂商的生产能力要求也开始降低,可以通过采购不同模块进行集成,很大程度优化了先进工艺的生产流程。

总的来看,Chiplet 工艺对于测试机的需求要高于 SOC 工艺。而测试机是具有非常高的技术壁垒,其关键点在于做数据处理的测试软件平台以及用于数据传输的内部板卡,这将会是测试机厂商的核心竞争力所在。

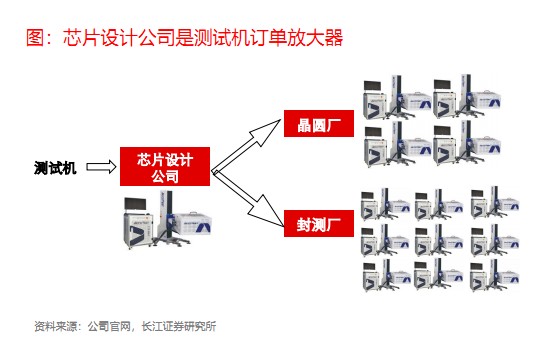

芯片设计是测试机订单先验者

从产业链生态环节来看,测试机的直接下游首先是芯片设计公司,再者是晶圆厂和封测厂,而后两者的采购量要远远高于前者。

芯片设计公司会先与自己的客户进行芯片需求沟通交流来设计方案,同时也会采购少量的测试机,通过了这个环节后,才会驱动才下游代工厂和封装厂进行采购。

最终下游的真实装机量是与设计公司以及客户数量构成完整的生态闭环。对于该生态来说,每一环都紧紧相扣,一旦通过客户认证则具备非常强的粘性。

风险提示及免责条款

市场有风险,投资需谨慎。本文不构成个人投资建议,也未考虑到个别用户特殊的投资目标、财务状况或需要。用户应考虑本文中的任何意见、观点或结论是否符合其特定状况。据此投资,责任自负。